# Technology Licensing & IP Management from APS Perspectives

Raymond Lim Director (IP & Technology) [Email: sslim@advanpack.com]

APSi

where *i*nnovation thrives...

## APS at a Glance

- First incorporated in 1996

- Knowledge-based company since 2005

- Industry Field:

- Business Activity:

- IP Protection:

Semiconductor IC Packaging Technology Innovation & Licensing Patents, Know-hows

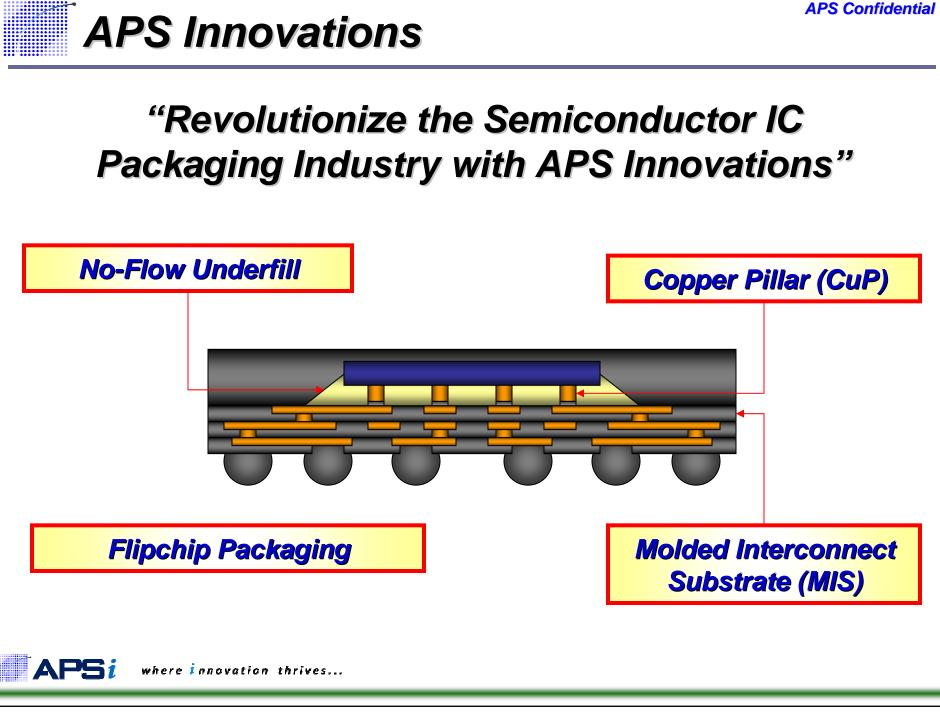

- Products / Technologies Developed:

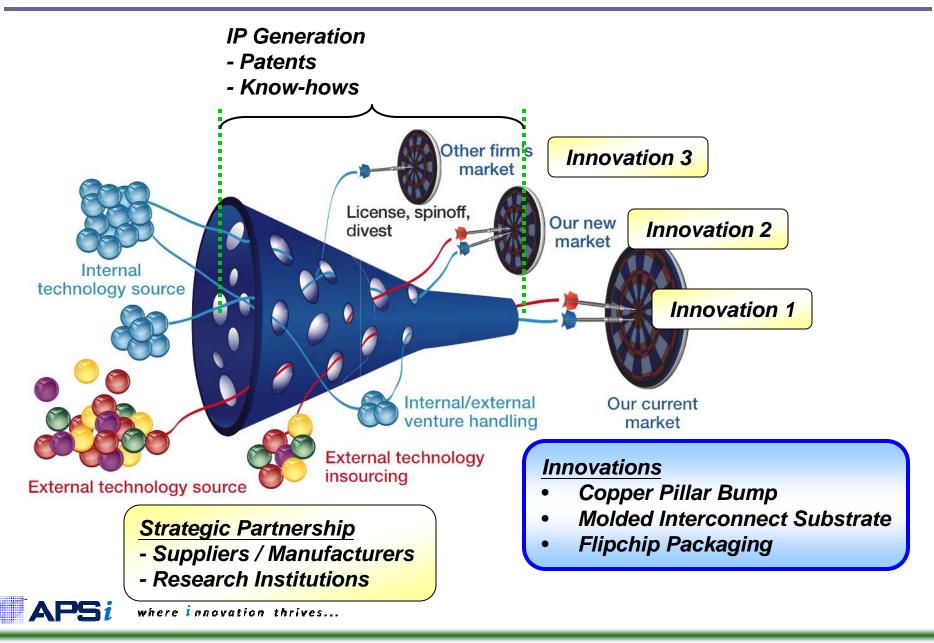

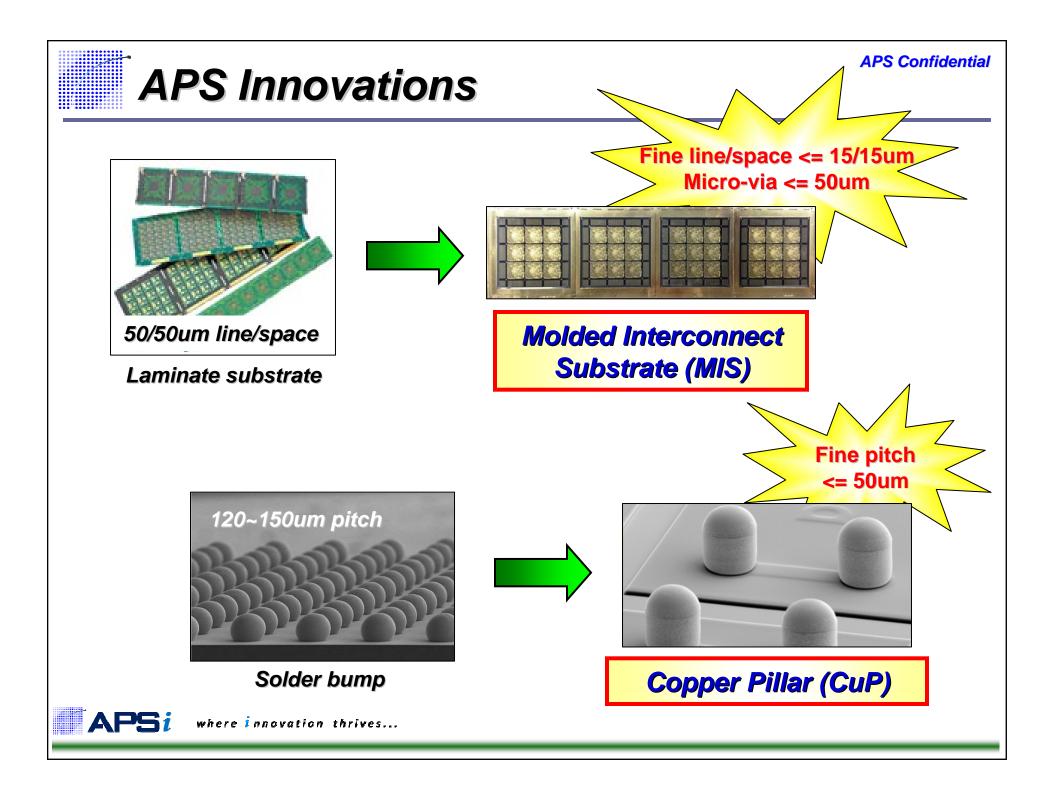

- Copper Pillar (CuP)

- Molded Interconnect Substrate (MIS)

- Flipchip Packaging

# "Revolutionize the Semiconductor IC Packaging Industry With APS Innovations"

where *i*nnovation thrives...

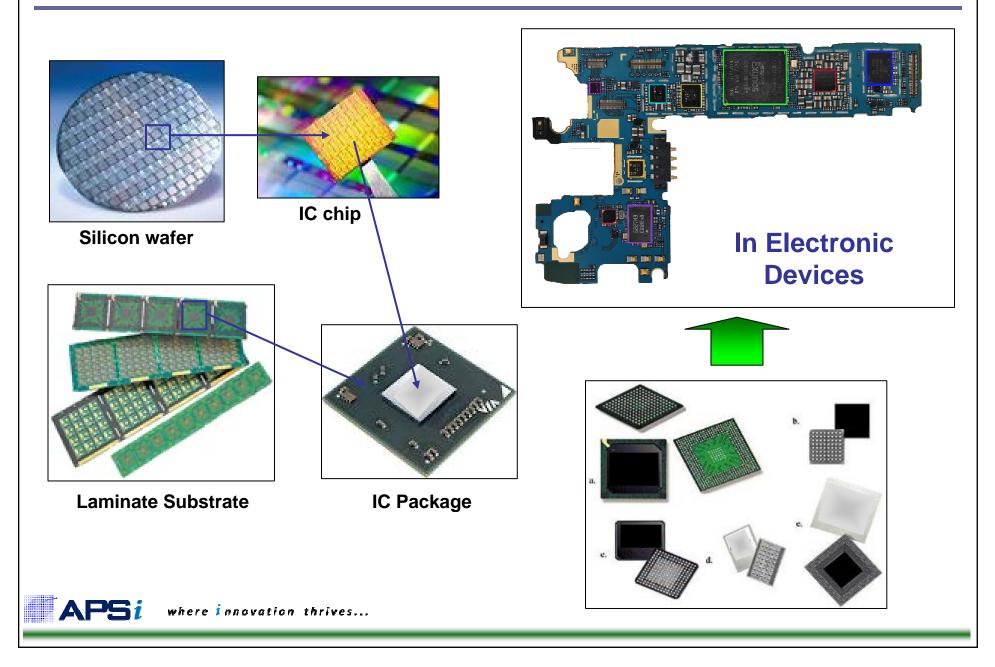

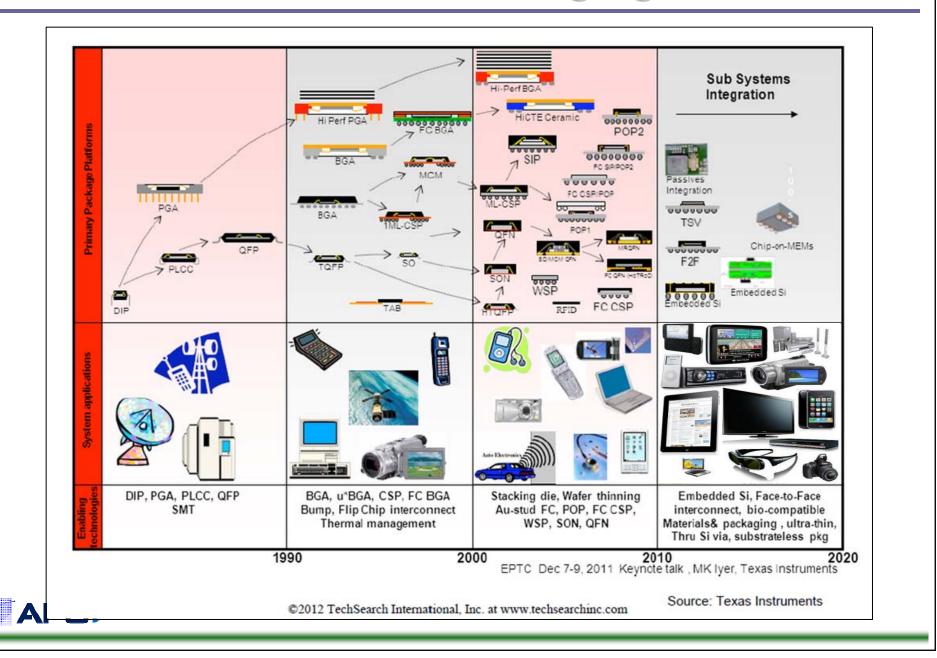

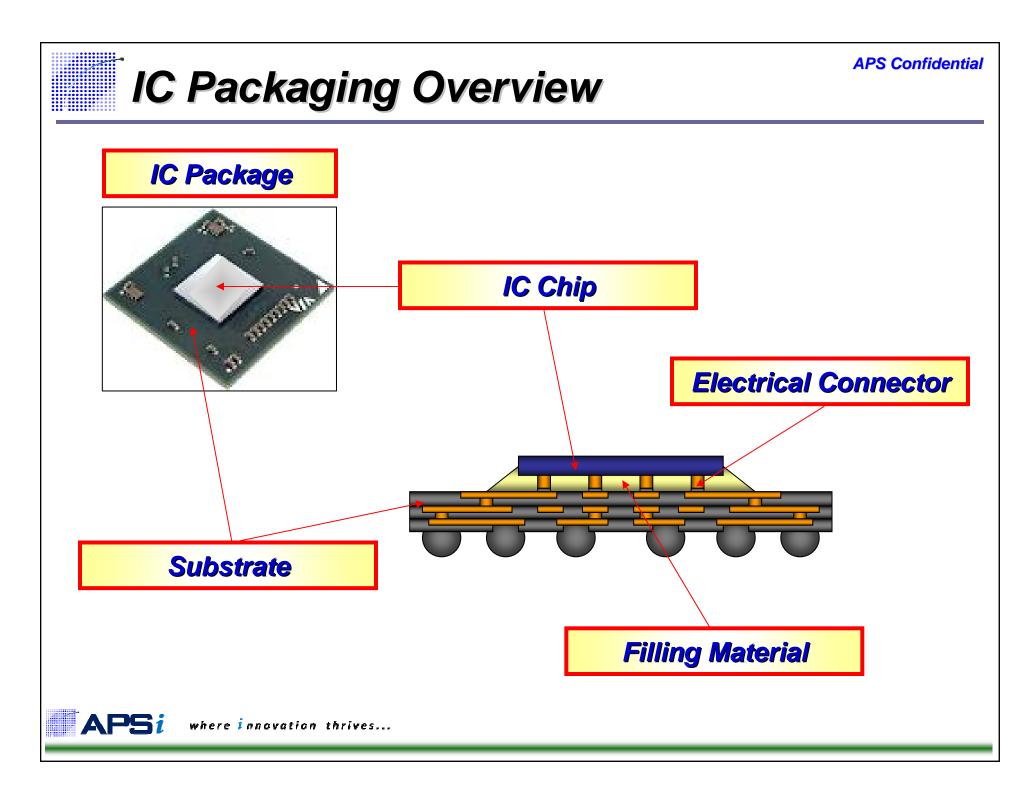

# IC Packaging Overview

## Semiconductor IC Packaging

"Technology + Intellectual Property"

Technology Know-hows

More than 100 Patent Applications

59 Patents Issued

42 Patents Pending

\*\*As of Dec 2013

where *i*nnovation thrives...

# **Open Innovation Model**

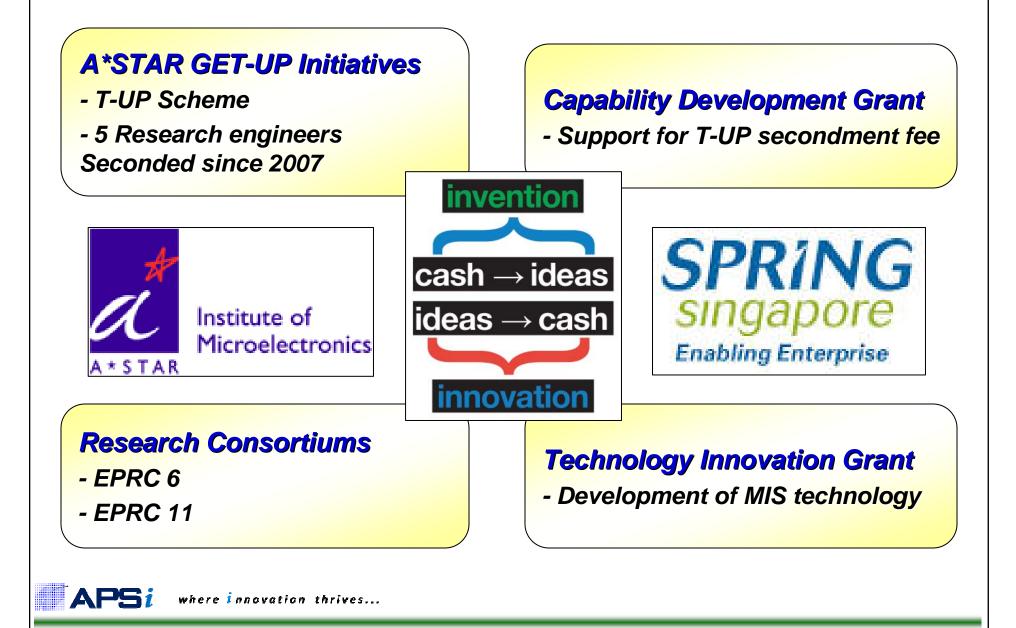

# **Funding & Capability Support**

## **APS** Patents

## **Copper Pillar** US pat. 6,578,754 Filed on Apr 27, 2000

##

6.369.451 B2 \* 4/2002 Lin

04037139

JP

(12) United States Patent Tung

(10) Patent No.: US 6,578,754 B1 (45) Date of Patent: Jun. 17, 2003

FOREIGN PATENT DOCUMENTS

OTHER PUBLICATIONS

"A fine pitch and high aspect ratio bump fabrication process

for flip-chip interconnection," by Yamada et al., Electronic Manuf. Tech. Symp., 1995, Proceedings of 1995 Japan Int'l

18th, IEEE/CPMT Int'l Omiya, Japan, Dec. 4-6, 1995, New

0602328 A2 9/1993 0889512 A2 4/1998 04037139 5/1992

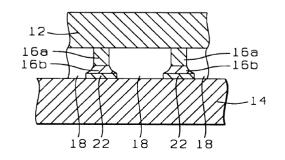

(54) PILLAR CONNECTIONS FOR SEMICONDUCTOR CHIPS AND METHOD OF MANUFACTURE

(75) Inventor: Francisca Tung, Austin, TX (US)

- (73) Assignce: Advanpack Solutions Pte. Ltd., Singapore (SG)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/564,382

- (22) Filed: Apr. 27, 2000

- (51) Int. CL7 ... .. B23K 35/14 (52) U.S. Cl. ... (58) Field of Search 643, 644, 570; 148/24; 106/286.2, 287.19 438/613-617: 257/737-738

- (56) References Cited

#### U.S. PATENT DOCUMENTS

4,705,205 A \* 11/1987 Allen et al. 5,075,965 A \* 12/1991 Carey et al. 5,130,779 A 7/1992 Agarwala et 5,234,974 5.334.804 A 5.536.362 A 7/1996 Love et al. ..... 156/643.1 773.889 A 6/1998 Love et al. ..... 6/1998 Wen et al. ...... 8/1998 Schreiber et al. 257/737 5,773,897 A 5,790,377 A ...... 257/778 5.807,766 A 9/1998 McBride .. .. 438/119 6.015.505 A \* 1/2000 David et al. 6,105,851 A \* 8/2000 Norell et al. 6,196,443 B1 \* 3/2001 DiGiacomo

York, NY, USA, IEEE, pp. 121–124 XP010195564. "Wire Interconnect Technology, a New High-Reliability Tight-Pitch Interconnect Technology," D. Love et al., Fijitsu Computer Packaging Technologies, Inc., ITAP (Interna tional TAB, Flip Chip and BGA Packaging Conference) Feb. 1996,, 7 pages \* cited by examiner Primary Examiner-Tom Dunn Assistant Examiner-Jonathan Johnson (74) Attorney, Agent, or Firm-George O. Saile; Stephen B. Ackerman (57) ABSTRACT

A flip chip interconnect system comprises and elongated pillar comprising two elongated portions, one portion including copper and another portion including solder. The portion including copper is in contact with the semiconduc-tor chip and has a length preferably of more than 55 microns to reduce the effect of  $\alpha$  particles from the solder from affecting electronic devices on the chip. The total length of the pillar is preferably in the range of 80 to 120 microns

9 Claims, 6 Drawing Sheets

## Molded Interconnect Substrate US pat. 7,795,071 Filed on Sep 14, 2007

(56)

##

(12) United States Patent Hwee-Seng Jimmy et al.

(54) SEMICONDUCTOR PACKAGE FOR FINE PITCH MINIATURIZATION AND MANUFACTURING METHOD THEREOF

(75) Inventors: Chew Hwee-Seng Jimmy, Singapore (SG); Ong Chee Kian, Singapore (SG); Abd. Razak Bin Chichik, Singapore (SG)

(73) Assignce: Advanpack Solutions Pte Ltd., Singapore (SG)

Subject to any disclaimer, the term of this (\*) Notice: patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 11/898,717

(22) Filed: Sep. 14, 2007

Prior Publication Data (65) US 2008/0145967 A1 Jun. 19, 2008

Related U.S. Application Data

(63) Continuation-in-part of application No. 11/882,194, filed on Jul. 31, 2007, now abandoned.

#### (30) Foreign Application Priority Data

Dec. 14, 2006 (TW) ...... 95146945 A (51) Int. Cl. H01L 21/00 (2006.01) 438/106; 257/666; 257/667; 257/673; 257/708; 257/710; 257/E23.01; (52) U.S. CL 257/E23.023; 257/E23.031; 257/E23.034; 257/E23.036; 438/111; 438/112 257/688, 690-691, 708, 710, 678, E23.01, 257/E23.023, E23.031, E23.034, E23.036, 257/E23.065, E23.06, E23.062, E23.07; 174/261-262; 361/820, 767, 777, 783, 770, 762, 679, 748 See application file for complete search history.

#### (10) Patent No.: US 7,795,071 B2 (45) Date of Patent: Sep. 14, 2010

**References** Cited U.S. PATENT DOCUMENTS

5.481.798 A \* 1/1996 Obsawa et al 29/827 5.608.265 A 3/1997 Kitano et al. 5,877,559 A 3/1999 Takayama et al. 6,528,869 B1 3/2003 Glenn et al. 6,563,202 B1 \* 5/2003 Ohsawa et al. ..... 257/673 6,784,376 B1 8/2004 Huemoeller et al. 2001/0017221 A1\* 8/2001 Horiuchi et al. ..... 174/260 2003/0045024 A1\* 3/2003 Shimoto et al. ..... 438/106 2003/0194855 A1 10/2003 Park et al. 2005/0088833 A1 4/2005 Kikuchi et al.

\* cited by examiner

(57)

Primary Examiner-A. Sefer Assistant Examiner-Ermias Woldegeorgis (74) Attorney, Agent, or Firm-Rabin & Berdo, PC

ABSTRACT

A semiconductor package and a manufacturing method thereof are provided. The package element has a first insulat ing layer, and a plurality of holes are disposed on the first surface of the first insulating layer. Besides, a plurality of package traces are embedded in the insulating layer and connected to the other end of the holes. The holes function as a positioning setting for connecting the solder balls to the package traces, such that the signal of the semiconductor chip is connected to the package trace via conductor of the chip, and further transmitted externally via solder ball. The elastic modulus of the material of the first insulating layer is preferably larger than 1.0 GPa.

#### 4 Claims, 11 Drawing Sheets

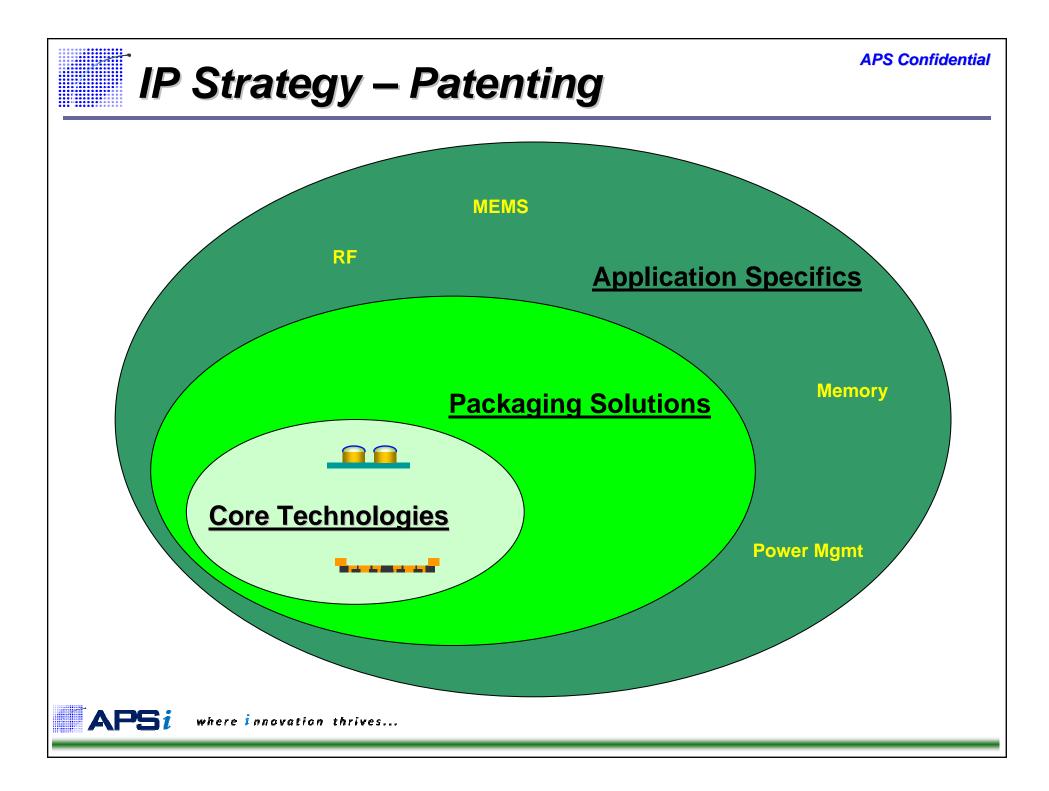

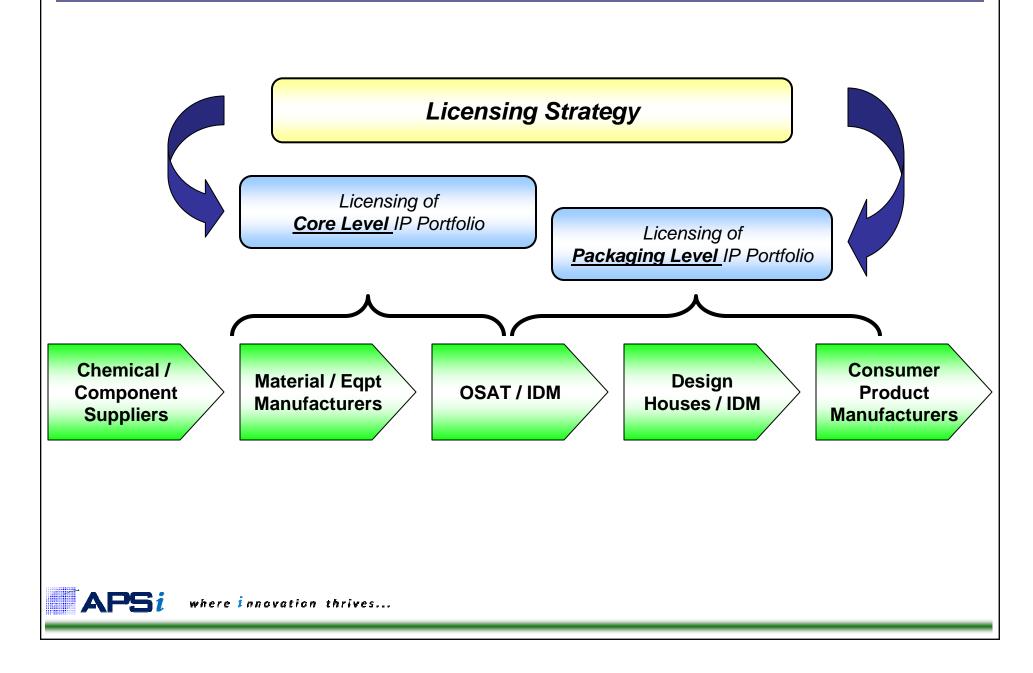

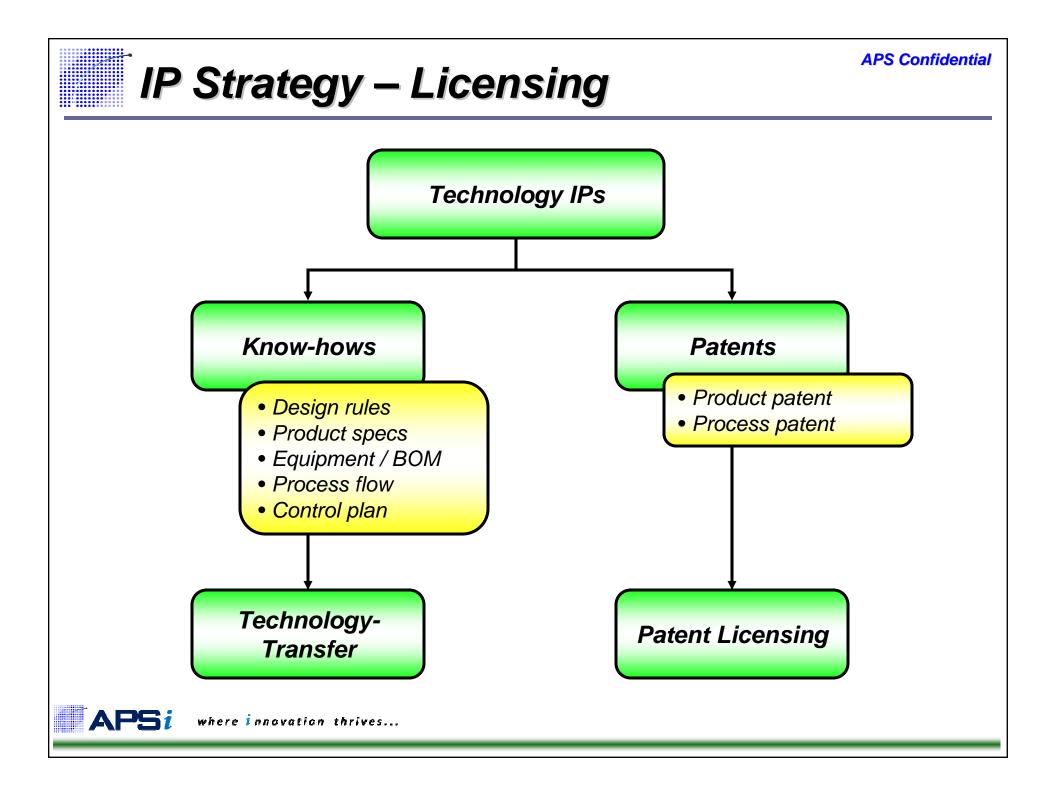

# IP Strategy – Licensing

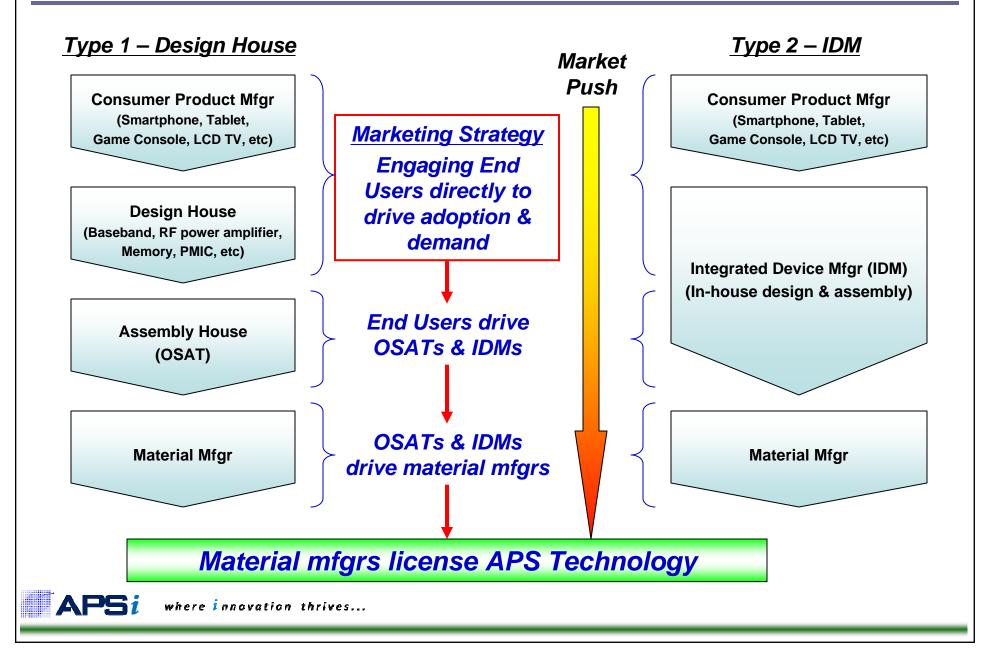

# Commercialization / Marketing Strategy

# **Commercialization / Marketing Strategy**

**APS***i* where *i*nnovation thrives...

### **APS Confidential Commercialization / Marketing Strategy**

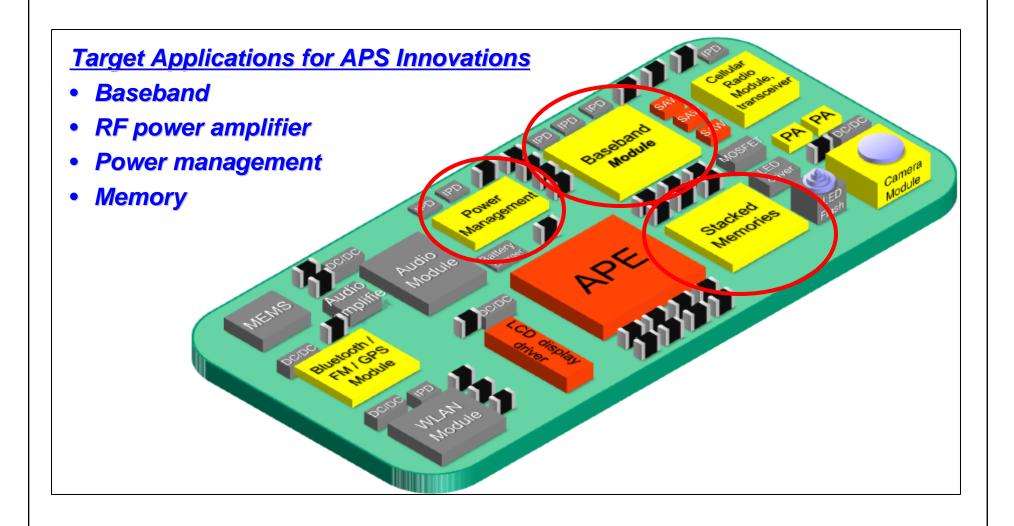

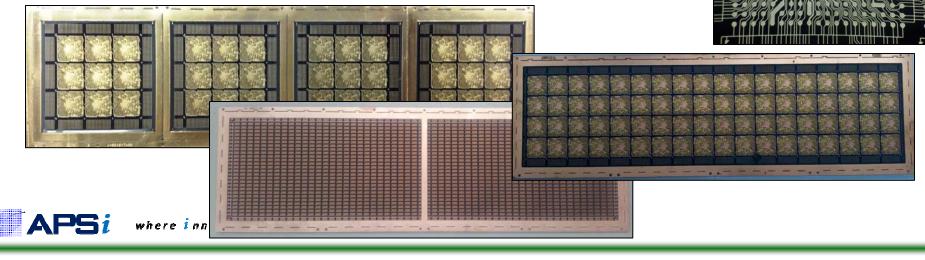

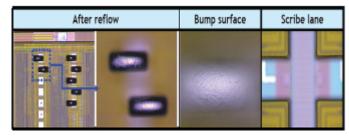

## **APS Innovations - MIS Substrate**

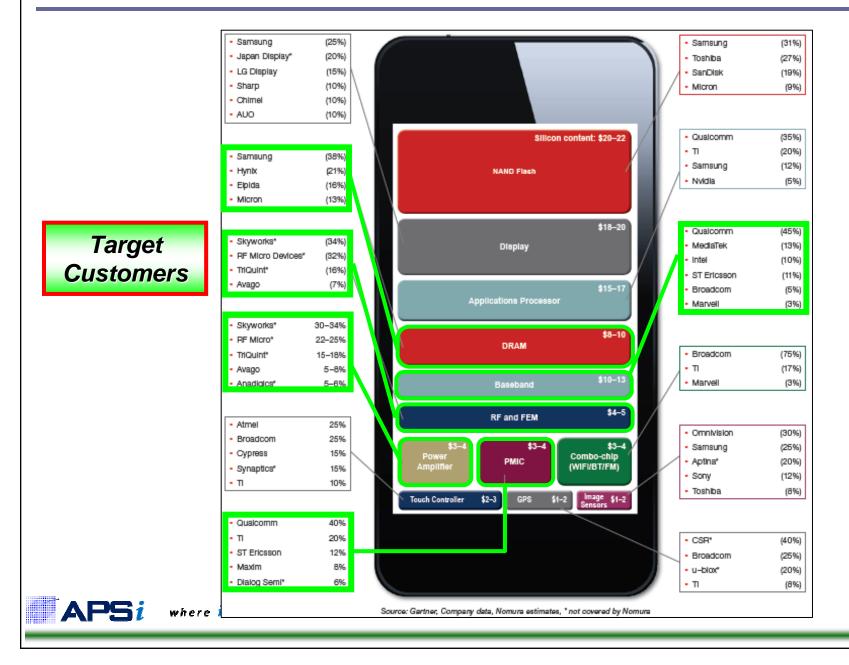

## Key Business Outcome to Date

- 5 Licensees

- 2 Licensees in Pipeline for 2014

- Technology Impact

- Revolutionize Semiconductor Substrate Industry

- Novel manufacturing concept

- Improve product features

- Reduce cost by 20~50%

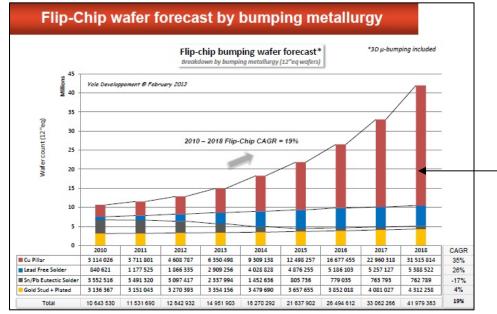

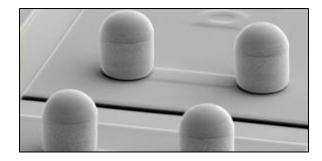

# **APS Innovations - CuP Bump**

## Key Business Outcome to Date

- 2 Joint Ventures

- In China

- In Malaysia

- 10 Licensees

Source: Yole Development

where *i*nnovation thrives...

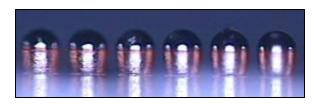

Pillar bump

Elongated pillar bump

## Pillar bump wafers

# **Thank You for Your Attention**

where *innovation* thrives...

APS<sub>i</sub>